Scientists have created the world’s tallest chip, composed of 41 layers. This “transistor skyscraper” overcomes the restrictions of Moore’s Legislation, efficiently boosting chip efficiency by six occasions.

The well-known speculation that has lengthy ruled the principles of the semiconductor world and enabled speedy technological development states: chips change into smaller, quicker, and denser with every new technology. In 1965, when built-in circuits had been nonetheless nascent, Gordon E. Moore predicted that the variety of elements on a single chip would roughly double each two years. Since then, a lot of our fashionable world—from computer systems and smartphones to cloud programs and big knowledge facilities—has progressed following this logic of “scaling all the way down to multiply.”

Nonetheless, right this moment, as transistors strategy the atomic scale, this steady shrinking recreation is hitting bodily limits resulting from quantum results. A world analysis workforce is now addressing this very threshold, suggesting that chips needs to be constructed upward, not horizontally.

A Design Completely different from Immediately’s Chips

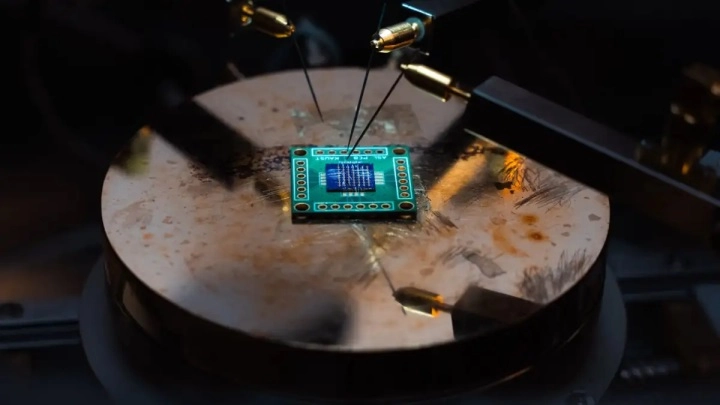

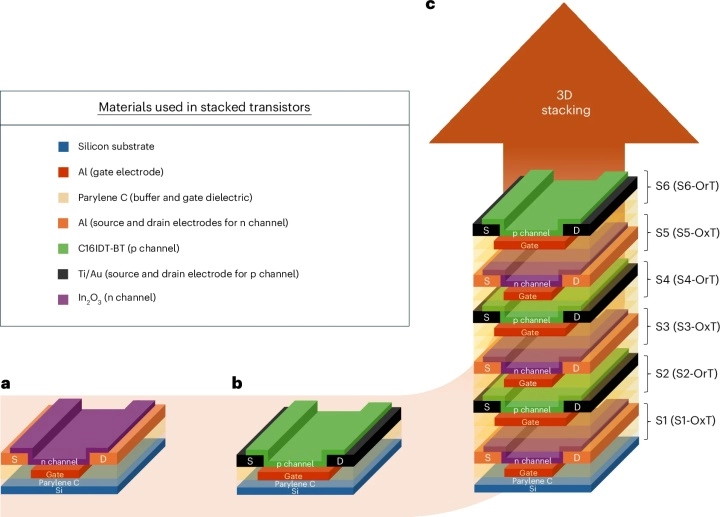

This analysis introduces a brand new semiconductor chip design consisting of 41 layers, every containing 100 transistors. This density is about ten occasions larger than that beforehand reported in stacked hybrid chips, making it the tallest chip ever constructed. This revolutionary design will increase circuit density by six-fold, enabling a efficiency increase with out the necessity for additional shrinking of the person transistors.

Immediately, processors like AMD’s Ryzen 7 9800X3D can supply extra cache by stacking chips on prime of one another. Equally, NAND reminiscence utilized in SSDs is constructed with dozens of layers. Nonetheless, these strategies are basically primarily based on single-layer transistor arrays. The brand new methodology developed by KAUST is the primary to beat this restrict by making a multi-layer transistor construction inside a single chip.

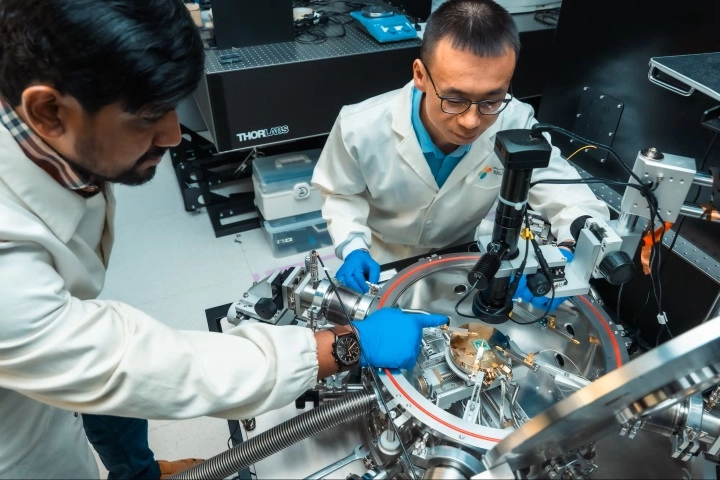

The workforce, led by KAUST researcher Xiaohang Li in Saudi Arabia, is offering a vertical resolution to the bodily limits approaching the semiconductor business. Based on the printed research, the workforce produced a chip manufactured from 41 semiconductor and insulator layers. Along with being the tallest chip ever produced, this construction is poised to allow versatile, energy-efficient, and sustainable digital programs.

Li states, “Vertically stacking six or extra transistor layers permits us to extend circuit density with out lowering the horizontal dimensions. With six layers, we are able to combine 600% extra logic features into the identical space in comparison with a single layer, thereby reaching larger efficiency and decrease energy consumption.”

Transistor Skyscrapers

The developed system is in comparison with a skyscraper. Similar to these large constructions, every layer within the chips should be constructed with excessive precision. The analysis workforce developed new manufacturing methods to resolve the difficulty of “interlayer roughness.” The researchers achieved a floor roughness of simply 3.63 nanometers in layer alignment. This stage of precision is essential to minimizing efficiency loss. Probably the most essential level was the low-temperature deposition of all layers at close to room-temperature circumstances.

This low-temperature manufacturing methodology isn’t just an engineering success; it additionally permits the usage of versatile supplies. Conventional semiconductor processes usually exceed 400°C, which melts or degrades plastic or polymer-based supplies. The brand new methodology eliminates this downside, permitting the protected use of plastic or polymer substrates, paving the best way for versatile electronics.

450 Instances Decrease Vitality Consumption!

To show the reliability of the design, the workforce produced 600 chips. All copies confirmed comparable efficiency, whereas the facility consumption was measured at solely 0.47 microwatts. For comparability, the worth in right this moment’s superior single-layer chips is round 210 microwatts. This implies the brand new design can carry out the identical operations with roughly 450 occasions decrease power consumption.

Li notes that the know-how will first be utilized in areas like wearable well being sensors, sensible tags, and versatile shows, the place low power consumption and mechanical flexibility are essential. In the long run, researchers predict that it may allow new ideas akin to large-area info processing programs or “digital skins.” These programs may concurrently carry out knowledge sensing, processing, and communication features on the floor of objects or constructions.

Alternatively, the brand new construction isn’t but appropriate for high-temperature processors, because the transistors can behave erratically above 50°C. Because of this wearable applied sciences are the preliminary goal.

Moore’s Legislation has lengthy been cited as “approaching its finish.” Nonetheless, this strategy by KAUST means that the legislation isn’t lifeless, however merely altering its “path.”

You May Additionally Like;

Observe us on TWITTER (X) and be immediately knowledgeable in regards to the newest developments…

Copy URL